在傳統(tǒng)的認(rèn)知中,軟件與硬件開發(fā)往往是線性的:先有芯片等硬件平臺(tái),再在其上進(jìn)行軟件開發(fā)。隨著摩爾定律逼近物理極限,芯片設(shè)計(jì)周期長、成本高企,以及系統(tǒng)復(fù)雜性的指數(shù)級(jí)增長,這種模式正面臨嚴(yán)峻挑戰(zhàn)。如今,以“左移”(Shift-Left)為核心理念,在硅芯片實(shí)際流片制造完成之前,甚至在架構(gòu)設(shè)計(jì)之初就啟動(dòng)并深度集成軟件開發(fā),已成為行業(yè)主流趨勢(shì)。這不僅是為了縮短產(chǎn)品上市時(shí)間,更是為了確保最終產(chǎn)品的性能、功耗和功能達(dá)到預(yù)期目標(biāo)。

一、 前置開發(fā)的核心驅(qū)動(dòng)力

- 時(shí)間與成本壓力:一次芯片流片(Tape-out)的成本動(dòng)輒數(shù)千萬美元,周期長達(dá)數(shù)月乃至一年以上。若等到芯片回片(Silicon Return)后再進(jìn)行軟件調(diào)試,一旦發(fā)現(xiàn)重大設(shè)計(jì)缺陷,將導(dǎo)致災(zāi)難性的返工和市場窗口的錯(cuò)失。前置軟件開發(fā)可以提前暴露硬件設(shè)計(jì)問題,將風(fēng)險(xiǎn)扼殺在搖籃中。

- 系統(tǒng)復(fù)雜性:現(xiàn)代SoC(片上系統(tǒng))集成了CPU、GPU、NPU、各種加速器及復(fù)雜互連網(wǎng)絡(luò),其軟硬件協(xié)同設(shè)計(jì)的復(fù)雜度前所未有。軟件,特別是操作系統(tǒng)、驅(qū)動(dòng)、固件和關(guān)鍵中間件,已成為定義芯片功能和體驗(yàn)的關(guān)鍵部分。

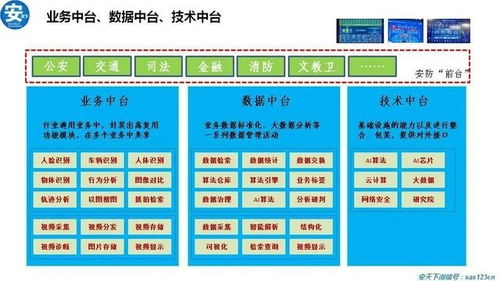

- 生態(tài)構(gòu)建:芯片的成功不僅取決于其自身性能,更依賴于其上的軟件生態(tài)。提前開發(fā)SDK(軟件開發(fā)工具包)、編譯器、庫函數(shù),并讓合作伙伴提前進(jìn)行應(yīng)用適配,能為芯片上市即用奠定堅(jiān)實(shí)基礎(chǔ)。

二、 關(guān)鍵技術(shù)與方法學(xué)

要在“虛擬”或“未完成”的硬件上進(jìn)行有效開發(fā),離不開一系列先進(jìn)工具鏈和方法學(xué)的支持:

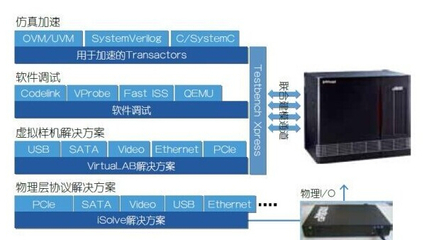

- 虛擬原型與仿真平臺(tái):

- 事務(wù)級(jí)模型(TLM)與虛擬平臺(tái):在寄存器傳輸級(jí)(RTL)設(shè)計(jì)完成前,使用SystemC等語言創(chuàng)建處理器和總線系統(tǒng)的高抽象級(jí)、高速仿真模型。軟件可以在這種“虛擬芯片”上全速或近全速運(yùn)行,進(jìn)行操作系統(tǒng)移植、驅(qū)動(dòng)開發(fā)和應(yīng)用程序早期測試。

- FPGA原型驗(yàn)證:將RTL代碼綜合到大規(guī)模FPGA板上,形成接近真實(shí)芯片性能的物理原型。這是進(jìn)行固件開發(fā)、性能分析和軟件壓力測試的黃金平臺(tái),速度遠(yuǎn)高于軟件仿真。

- 仿真與模擬器:

- 指令集模擬器(ISS):精確模擬處理器的指令執(zhí)行行為,是編譯器優(yōu)化、操作系統(tǒng)啟動(dòng)代碼開發(fā)的關(guān)鍵工具。

- RTL仿真:雖然速度慢,但精度最高。可用于調(diào)試與硬件交互最緊密的底層軟件(如啟動(dòng)引導(dǎo)代碼、低層驅(qū)動(dòng)),確保軟件對(duì)硬件寄存器的操作絕對(duì)正確。

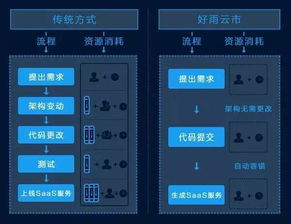

- 云化與平臺(tái)化:將上述虛擬原型、FPGA原型等資源池化,通過云平臺(tái)提供給內(nèi)部及外部開發(fā)團(tuán)隊(duì)。開發(fā)者可以遠(yuǎn)程訪問、分配和復(fù)用這些資源,實(shí)現(xiàn)軟硬件開發(fā)的并行與協(xié)同,極大提升效率。

- 模型驅(qū)動(dòng)與敏捷實(shí)踐:

- 采用基于模型的系統(tǒng)工程(MBSE)方法,從統(tǒng)一的功能需求模型同時(shí)衍生出硬件架構(gòu)規(guī)約和軟件需求規(guī)約。

- 在軟件團(tuán)隊(duì)內(nèi)部,實(shí)施敏捷開發(fā)(如Scrum),以可運(yùn)行的軟件增量(即便在虛擬平臺(tái)上運(yùn)行)作為迭代目標(biāo),持續(xù)集成和驗(yàn)證。

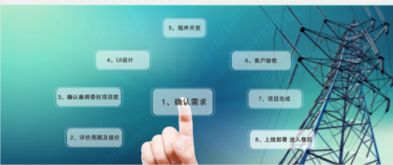

三、 軟件開發(fā)流程的前置整合

- 架構(gòu)探索階段:軟件架構(gòu)師與硬件架構(gòu)師共同工作,基于性能建模和功耗分析工具,評(píng)估不同架構(gòu)對(duì)目標(biāo)工作負(fù)載(如AI推理、圖形渲染)的影響。軟件的需求(如任務(wù)調(diào)度策略、內(nèi)存管理需求)直接反饋給硬件設(shè)計(jì)。

- RTL開發(fā)與驗(yàn)證階段:

- 驅(qū)動(dòng)和固件團(tuán)隊(duì)開始基于TLM模型或早期RTL進(jìn)行開發(fā)。

- 操作系統(tǒng)內(nèi)核移植工作啟動(dòng)。

- 開發(fā)基本的診斷和測試軟件,用于后續(xù)的硬件驗(yàn)證。

- 原型驗(yàn)證階段:

- 在FPGA原型上,進(jìn)行全面的軟件棧集成測試,包括啟動(dòng)、驅(qū)動(dòng)、中間件和代表性應(yīng)用。

- 進(jìn)行性能剖析與優(yōu)化,發(fā)現(xiàn)硬件瓶頸并為最終芯片的時(shí)鐘頻率、緩存大小等提供決策依據(jù)。

- 流片后至回片前:

- 軟件持續(xù)在仿真和原型環(huán)境上迭代和穩(wěn)定化。

- 準(zhǔn)備量產(chǎn)所需的全部軟件鏡像、工具和文檔。

四、 面臨的挑戰(zhàn)

- 模型精度與速度的權(quán)衡:高抽象級(jí)模型快但不夠精確,可能掩蓋細(xì)節(jié)問題;低層次模型精確但慢,影響開發(fā)效率。需要根據(jù)開發(fā)階段選擇合適的平臺(tái)。

- 工具鏈的成熟度與整合:整個(gè)流程涉及多家供應(yīng)商的多種工具(仿真、調(diào)試、性能分析),其間的數(shù)據(jù)互通和流程整合是一大挑戰(zhàn)。

- 跨領(lǐng)域團(tuán)隊(duì)協(xié)作:要求軟件工程師具備一定的硬件知識(shí),硬件工程師理解軟件影響,對(duì)團(tuán)隊(duì)文化和溝通機(jī)制提出高要求。

- 驗(yàn)證完備性:如何確保在非真實(shí)硬件上測試的軟件,在真實(shí)芯片上能萬無一失,仍需大量的交叉驗(yàn)證和回歸測試。

###

“硅未至而碼已行”已成為芯片行業(yè),特別是高性能計(jì)算、人工智能、自動(dòng)駕駛等前沿領(lǐng)域的標(biāo)準(zhǔn)實(shí)踐。它不僅僅是一種技術(shù)手段的革新,更是一種產(chǎn)品開發(fā)范式的根本性轉(zhuǎn)變——從硬件主導(dǎo)的串聯(lián)模式,走向軟硬件深度協(xié)同、并行開發(fā)的融合模式。成功駕馭這一模式的企業(yè),將能在激烈的市場競爭中贏得至關(guān)重要的時(shí)間窗口,并交付體驗(yàn)更優(yōu)、缺陷更少的產(chǎn)品。隨著數(shù)字孿生、AI輔助設(shè)計(jì)等技術(shù)的發(fā)展,軟硬件的協(xié)同設(shè)計(jì)與開發(fā)將更加智能和無縫。